Visible to Intel only — GUID: uuc1472825634779

Ixiasoft

1. Intel® HLS Compiler Pro Edition Reference Manual

2. Compiler

3. C Language and Library Support

4. Component Interfaces

5. Component Memories (Memory Attributes)

6. Loops in Components

7. Component Concurrency

8. Arbitrary Precision Math Support

9. Component Target Frequency

10. Systems of Tasks

11. Libraries

12. Advanced Hardware Synthesis Controls

13. Intel® High Level Synthesis Compiler Pro Edition Reference Summary

A. Advanced Math Source Code Libraries

B. Supported Math Functions

C. Cyclone® V Restrictions

D. Intel® HLS Compiler Pro Edition Reference Manual Archives

E. Document Revision History of the Intel® HLS Compiler Pro Edition Reference Manual

6.1. Loop Initiation Interval (ii Pragma)

6.2. Loop-Carried Dependencies (ivdep Pragma)

6.3. Loop Coalescing (loop_coalesce Pragma)

6.4. Loop Unrolling (unroll Pragma)

6.5. Loop Concurrency (max_concurrency Pragma)

6.6. Loop Iteration Speculation (speculated_iterations Pragma)

6.7. Loop Pipelining Control (disable_loop_pipelining Pragma)

6.8. Loop Interleaving Control (max_interleaving Pragma)

6.9. Loop Fusion

11.4.1.1. Integration of an RTL Module into the HLS Pipeline

11.4.1.2. RTL Module Interfaces

11.4.1.3. RTL Reset and Clock Signals

11.4.1.4. Object Manifest File Syntax

11.4.1.5. Mapping HLS Data Types to RTL Signals

11.4.1.6. HLS Emulation Models for RTL-Based Functions

11.4.1.7. Potential Incompatibility between RTL Modules and Partial Reconfiguration

11.4.1.8. Stall-Free RTL

11.4.1.9. RTL Module Restrictions and Limitations for HLS Libraries

13.1. Intel® HLS Compiler Pro Edition i++ Command-Line Arguments

13.2. Intel® HLS Compiler Pro Edition Header Files

13.3. Intel® HLS Compiler Pro Edition Compiler-Defined Preprocessor Macros

13.4. Intel® HLS Compiler Pro Edition Keywords

13.5. Intel® HLS Compiler Pro Edition Simulation API (Testbench Only)

13.6. Intel® HLS Compiler Pro Edition Component Memory Attributes

13.7. Intel® HLS Compiler Pro Edition Loop Pragmas

13.8. Intel® HLS Compiler Pro Edition Scope Pragmas

13.9. Intel® HLS Compiler Pro Edition Component Attributes

13.10. Intel® HLS Compiler Pro Edition Component Default Interfaces

13.11. Intel® HLS Compiler Pro Edition Component Invocation Interface Control Attributes

13.12. Intel® HLS Compiler Pro Edition Component Macros

13.13. Intel® HLS Compiler Pro Edition Systems of Tasks API

13.14. Intel® HLS Compiler Pro Edition Pipes API

13.15. Intel® HLS Compiler Pro Edition Streaming Input Interfaces

13.16. Intel® HLS Compiler Pro Edition Streaming Output Interfaces

13.17. Intel® HLS Compiler Pro Edition Memory-Mapped Interfaces

13.18. Intel® HLS Compiler Pro Edition Load-Store Unit Control

13.19. Intel® HLS Compiler Pro Edition Arbitrary Precision Data Types

B.1. Math Functions Provided by the math.h Header File

B.2. Math Functions Provided by the extendedmath.h Header File

B.3. Math Functions Provided by the ac_fixed_math.h Header File

B.4. Math Functions Provided by the hls_float.h Header File

B.5. Math Functions Provided by the hls_float_math.h Header File

B.6. Default Rounding Schemes and Subnormal Number Support

Visible to Intel only — GUID: uuc1472825634779

Ixiasoft

4.1.4. Interface Definition Example: Component with Both Scalar and Pointer Arguments

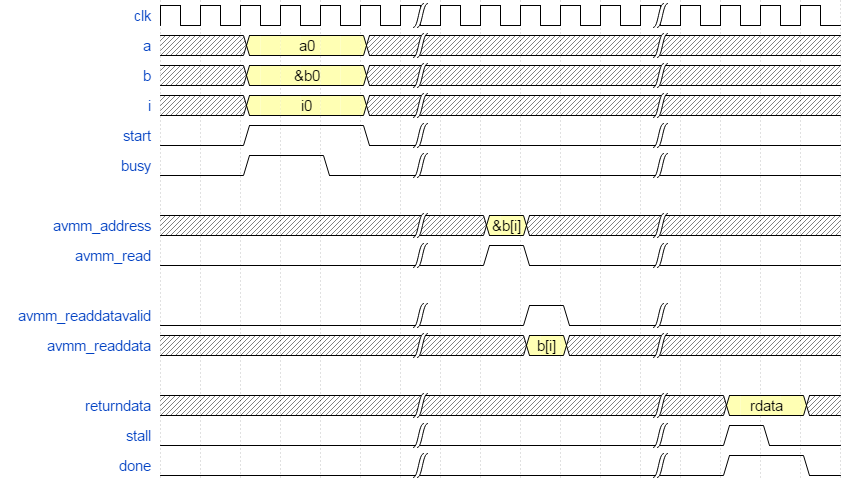

The following design example illustrates the interactions between a component's interfaces and signals, and the waveform of the corresponding RTL module.

component int dut(int a, int* b, int i) {

return a*b[i];

}

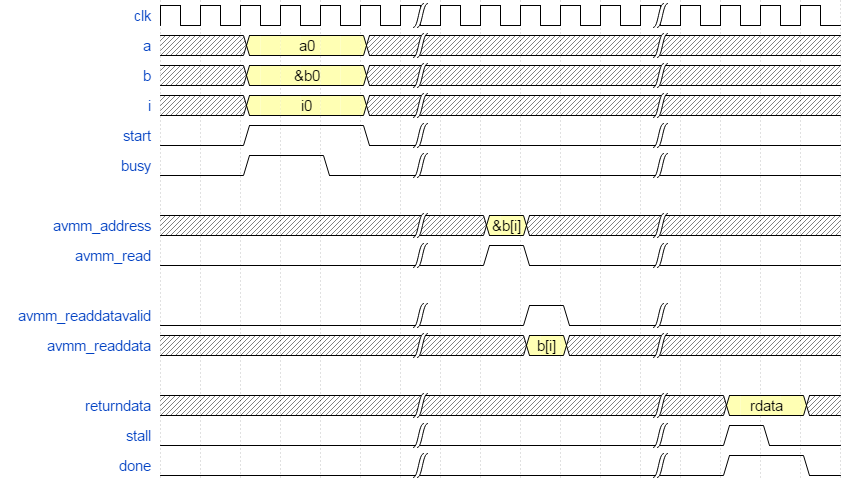

Figure 2. Block Diagram of the Interfaces and Signals for the Component dut

Figure 3. Waveform Diagram of the Signals for the Component dutThis diagram shows that the Avalon-MM read signal reads from a memory interface that has a read latency of one cycle and is non-blocking.

If the dut component raises the busy signal, the caller needs to keep the start signal high and continue asserting the input arguments. Similarly, if the component downstream of dut raises the stall signal, then dut holds the done signal high until the stallsignal is de-asserted.