Visible to Intel only — GUID: zky1508966392162

Ixiasoft

Visible to Intel only — GUID: zky1508966392162

Ixiasoft

1.13.3. Transceiver Channel Placement Optimization

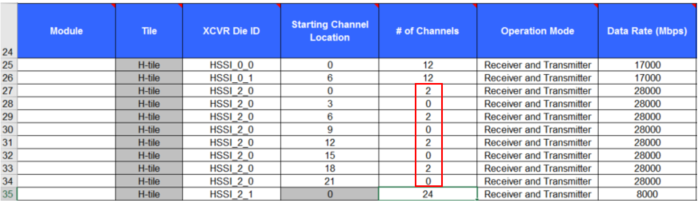

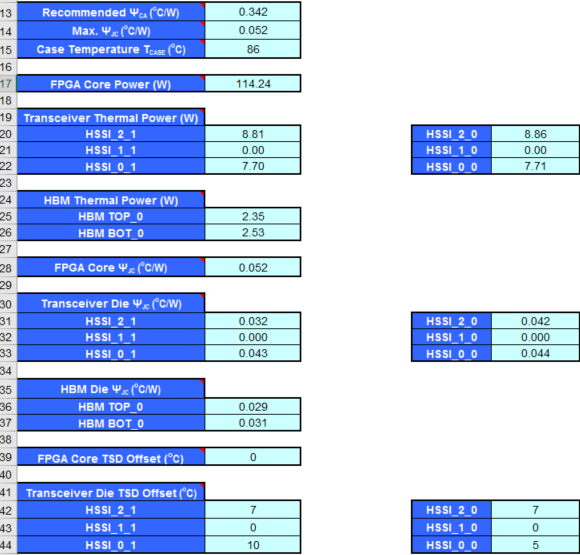

In some designs, it might be possible to further reduce the transceiver temperatures by spreading the channels to reduce the power density. For example, in the above design the HSSI_2_0 transceiver has 8 high speed transceiver channels that are laid out in half of the die. The effect of spreading these channels to all the die area can be shown in the EPE by the following transceiver placement.

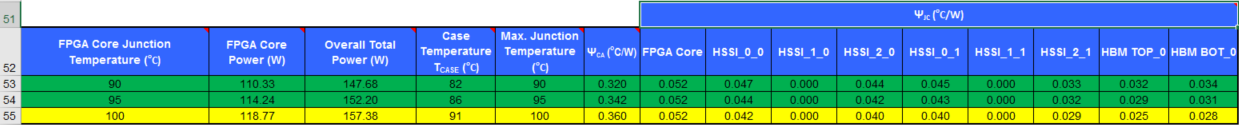

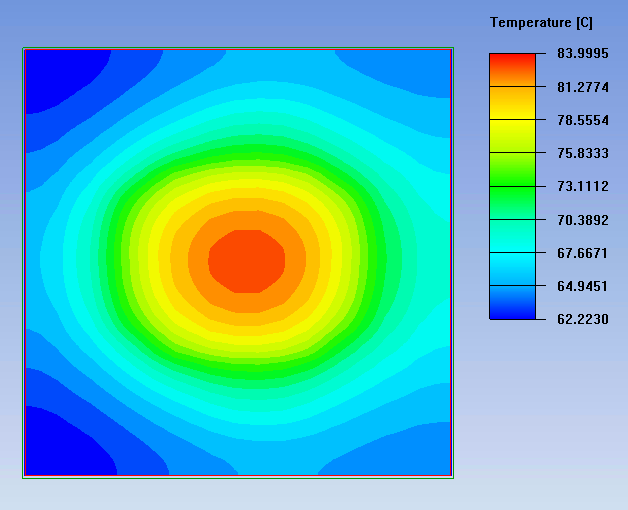

The new placement relaxes the cooling requirement from a ΨCA of 0.332 to 0.342 °C/W and now the core fabric die has the highest ΨJC. Repeating the CFD analysis using the original cooling solution with the new power dissipations results in the following IHS temperature results.

Calculating the new junction temperatures with the updated power values and CFD results:

HSSI_2_0 die temperature: TJ = 84 + (150 * 0.042) = 90.3 °C

Core fabric temperature: TJ = 84 + (150 * 0.052) = 91.8 °C

This example demonstrates that the channel spreading could reduce the cooling requirement or result in lower junction temperatures for the same cooling solution.